新智元报道

编辑:编辑部 XZH

英伟达,亲手打破了自己的天花板!刚刚,Blackwell 单用户每秒突破了 1000 个 token,在 Llama 4 Maverick 模型上,再次创下了 AI 推理的世界纪录。在官博中,团队放出了不少绝密武器。

你以为,AI 推理的速度已经够快了?

不,英伟达还能再次颠覆你的想象——就在刚刚,他们用 Blackwell 创下了 AI 推理的新纪录。

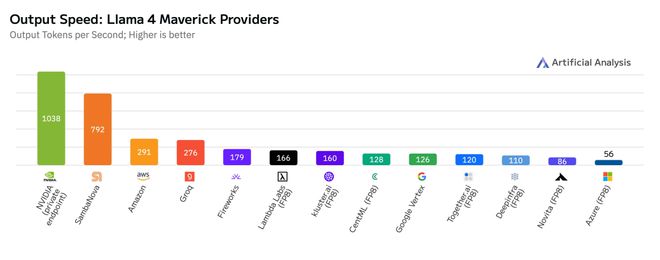

仅仅采用单节点(8 颗 Blackwell GPU)的 DGX B200 服务器,英伟达就实现了 Llama 4 Maverick 模型每秒单用户生成 1000 个 token(TPS/user)的惊人成绩!

单节点使用 8 块 B200 GPU

这项速度记录,由 AI 基准测试服务 Artificial Analysis 独立测量。

而且,更令人咋舌的是,单台服务器(GB200 NVL72,配备 72 颗 Blackwell GPU)的整体吞吐量,已经达到了 72,000 TPS!

GB200 NVL72 液冷机架原型机

这场速度革命的幕后,是一整套精心布局的技术组合拳——

-

使用 TensorRT-LLM 优化框架和 EAGLE-3 架构训练推测解码草稿模型;

-

在 GEMM、MoE 及 Attention 计算中全面应用 FP8 数据格式,有效缩小模型体积并提高计算效率;

-

应用 CUDA 内核优化技术(如空间分区、GEMM 权重重排、Attention 内核并行优化、程序化依赖启动(PDL)等);

-

运算融合(如 FC13+SwiGLU、FC_QKV+attn_scaling、AllReduce+RMSnorm 融合)。

由此,Blackwell 的性能潜力彻底被点燃,一举实现了 4 倍加速,直接把之前的最强 Blackwell 基线甩在身后!

迄今测试过最快 Maverick 实现

这次优化措施在保持响应准确度的同时,显著提升了模型性能。

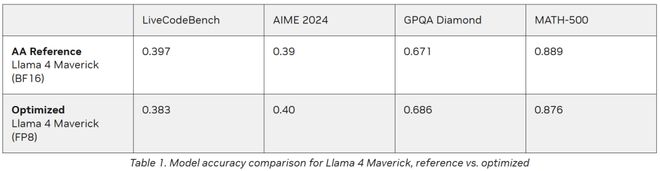

英伟达针对 GEMM(通用矩阵乘法)、MoE(混合专家模型)及 Attention(注意力)运算运用了 FP8 数据类型,旨在减小模型体积,并充分利用 Blackwell Tensor Core 技术所带来的高 FP8 吞吐量优势。

如下表所示,采用 FP8 数据格式后,模型在多项评估指标上的准确度可与 Artificial Analysis 采用 BF16 数据格式(进行测试)所达到的准确度相媲美:

为何减少延迟至关重要?

大部分用生成式 AI 的场景,都要在吞吐量(throughput)和延迟(latency)之间找一个平衡点,好让很多用户同时使用时,都能有个「还不错」的体验。

但是,有些关键场景,比如要迅速做出重要决策的时候,「响应速度」就变得特别重要,哪怕一点延迟都可能带来严重后果。

无论你想要的是同时处理尽可能多的请求,还是希望既能处理很多请求、响应又比较快,还是只想最快地服务单个用户(即最小化单个用户的延迟),Blackwell 的硬件都是最佳选择。

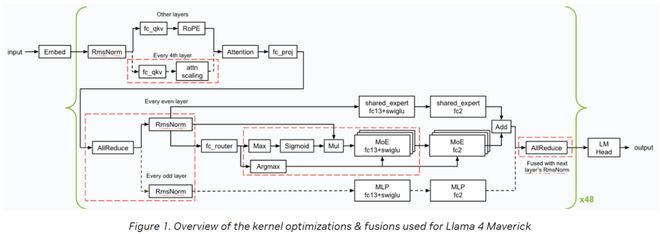

下图概述了英伟达在推理过程中应用的内核优化和融合(以红色虚线框标示)。

英伟达实现了若干低延迟 GEMM 内核,并应用了各种内核融合(如 FC13+SwiGLU、FC_QKV+attn_scaling 以及 AllReduce+RMSnorm),从而使 Blackwell GPU 在最小延迟场景下表现出色。

CUDA 内核优化与融合

在内核优化与融合方面,英伟达采用了以下几项关键技术:

-

空间分区与高效内存加载

利用空间划分(也称为 warp 专业化)并设计 GEMM 内核,可以高效的方式从内存中加载数据,从而最大限度地利用 NVIDIA DGX 所提供的巨大内存带宽——总计 64TB/s。

-

GEMM 权重重排

将 GEMM 权重以一种优化的 swizzled 格式进行重排。

由此可以确保在使用 Blackwell 第五代 Tensor Core 完成矩阵乘法计算后,从 Tensor 内存加载计算结果时能够获得更理想的数据布局。

-

Attention内核并行优化

通过沿K和V张量的序列长度维度对计算进行划分,优化了 Attention 内核的性能,使得计算任务能够在多个 CUDA 线程块上并行执行。

此外,还利用分布式共享内存机制,在同一线程块集群内的不同线程块之间高效地进行结果规约,从而避免了访问全局内存的需要。

-

运算融合

通过启用不同运算之间的融合,来减少内核执行间的开销以及内存加载/存储的次数。

例如,将 AllReduce 运算与紧随其后的 RMSNorm 运算及量化(Quantize)运算融合成单一的 CUDA 内核,以及将 SwiGLU 运算与其前置的 GEMM 运算进行融合。

程序化依赖启动(PDL)

程序化依赖启动(PDL)是一项 CUDA 功能,它能够减少同一 CUDA 流上两个连续 CUDA 内核执行之间的 GPU 空闲时间,甚至允许这两个内核部分重叠执行。

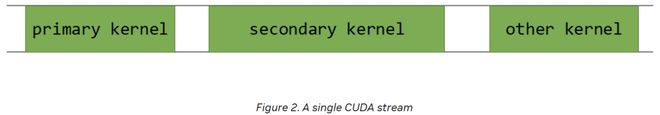

默认情况下,当多个内核在同一个 CUDA 流上启动时,第二个内核必须等待第一个内核执行完毕后才能开始。

这种机制会导致两个主要的性能问题:

-

其一,两个连续的内核执行之间会产生微小的间隙(如下图所示),在此期间 GPU 处于闲置状态。

-

其二,当第一个内核的执行接近尾声时,它可能仍会占用一部分流式多处理器(SM)来完成剩余的 CUDA 块计算,这使得 GPU 上的其他 SM 处于空闲,从而导致 GPU 整体计算能力的利用率不足。

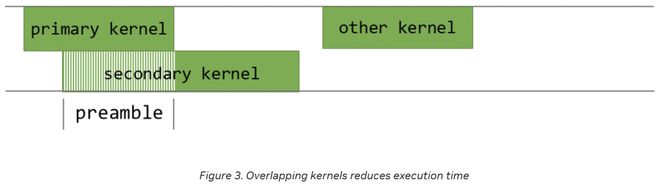

通过在 CUDA 中运用程序化依赖启动 API,英伟达允许次级内核(secondary kernel)在主内核(primary kernel)仍在运行时就开始执行。

在初始准备阶段(preamble period),次级内核可以执行那些不依赖于主内核执行的计算任务,并加载相应的数据。

这不仅消除了两个连续内核之间的执行间隙,也显著提升了 GPU 的利用率;因为当主内核仅占用 GPU 上的部分 SM 时,其余空闲的 SM 便可以开始运行次级内核。

推测解码

推测解码(Speculative Decoding)是一种广受欢迎的技术,用于在不牺牲生成文本质量的前提下,加速 LLM 的推理速度。

该技术通过一个规模更小、速度更快的「草稿」模型来预测一个推测 token 序列,然后由规模更大(通常也更慢)的 LLM 并行验证这些 token。

其加速效果源于:在目标模型的一次迭代中,有机会生成多个 token,代价则是草稿模型带来的一些额外开销。

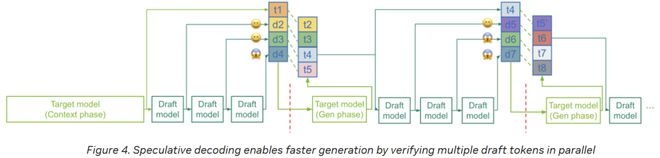

端到端的工作流

首先,在目标模型完成上下文阶段(此阶段亦会生成 token t1)之后,草稿模型会迅速生成一连串潜在的 token(例如 d2-d4)。

随后,目标模型进入生成阶段,在这一阶段,它会针对整个草稿序列,一次性地并行验证(或生成)每个位置的下一个 token。

如图所示,如果草稿 token 与目标模型自身将要生成的 token 相匹配,目标模型便可能「接受」其中的若干 token(如 d2、d3),同时「拒绝」其他的 token(如 d4)。

这个循环不断重复:被接受的 token 得以保留;若发生拒绝(例如,在 d4 被拒绝后),目标模型会提供正确的下一个 token(如 t4);然后,草稿模型会生成一个新的推测序列(例如 d5-d7)。

通过并行验证多个 token——而不是依赖(速度较慢的)目标模型逐个生成它们——并充分利用草稿模型的快速推测能力,系统能够实现显著的速度提升,尤其是当草稿模型的预测准确率较高时。

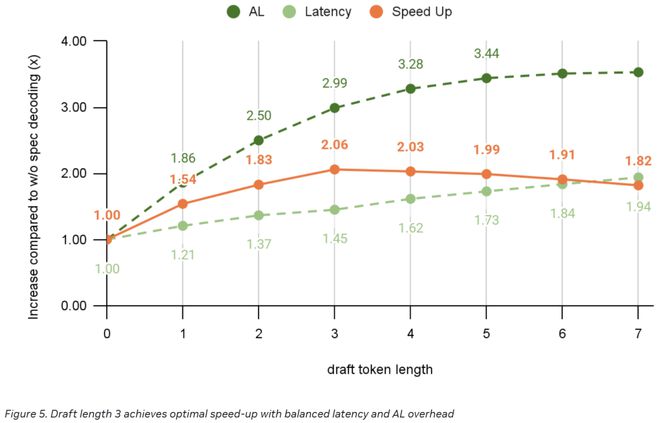

「接受长度(AL)」定义为在单次验证步骤中,平均能够成功生成的 token 数量。

AL 值越高,加速效果越显著。

对此,英伟达采用了一种基于 EAGLE3 的架构作为其推测解码方法,主要通过调整推测层中前馈网络(FFN)的大小来优化接受长度(AL)。

在推理过程中,需要在目标模型的前向传播阶段记录低、中、高三个层级的特征(即初始、中间及末端解码层输出的隐藏状态)。

之后,再将这些隐藏状态与 token 嵌入相结合,并将结果输入到推测层。该推测层随后以自回归方式生成一个草稿 token 序列,供目标模型进行并行验证。

推测层的开销虽然不大,但也不可忽视。因此,关键的挑战在于如何在草稿长度与端到端加速效果之间取得理想的平衡。

草稿长度越长,AL 通常也越高,但相应地,运行草稿模型所产生的额外成本也会增加。根据英伟达在下方实验中展示的结果,当草稿长度设置为 3 时,可获得最佳的加速效果。

通过 CUDA Graph 和重叠调度器减少主机端开销

推测解码的另一个挑战在于减少主模型与草稿模型之间的通信和同步开销。

如果英伟达将采样/验证逻辑置于主机端,便会在主机与设备之间引入额外的同步点,进而破坏 CUDA Graph 的完整性。

因此,英伟达选择将验证逻辑保留在设备端,从而能够将目标模型的前向传播、验证逻辑以及草稿模型的前向传播都整合到同一个 CUDA Graph 中。

此外,英伟达还启用了 TensorRT-LLM 的重叠调度器,以进一步让当前迭代的模型前向传播与下一次迭代的输入准备及 CUDA Graph 启动过程实现重叠。

使用 torch.compile ()优化草稿模型层

由于验证逻辑是采用 Torch 原生操作在设备端实现的,这导致英伟达最终生成了大量细小的 Torch 原生内核。

手动融合这些内核不仅复杂,且容易出错。

为此,英伟达采用 torch.compile (),借助 OpenAI Triton 的能力来自动完成这部分内核的融合,并生成最优化的版本。

这一举措帮助英伟达将草稿模型的开销从 25% 成功降低到了 18%(当草稿长度为 3 时)。

总结

总的来说,这一创世界纪录的速度,是强大 Blackwell 架构、自 CUDA 层面起直至上层应用的深度软件优化,以及英伟达量身定制的推测解码实现所带来的显著加速三者结合的成果,它直接响应了下一代 AI 交互应用对低延迟的迫切需求。

正如英伟达所展示的那样,这些技术进步确保了即便是超大规模模型,也能够提供足够的处理速度和响应能力,以支持无缝的实时用户体验和复杂的 AI 智能体部署场景。

作者介绍

Yilin Fan

Yilin Fan 是英伟达的高级深度学习工程师,专注于 TensorRT/TensorRT-LLM 的性能。

他拥有卡内基梅隆大学的软件工程硕士学位和北京航空航天大学的学士学位。

在加入英伟达之前,他曾在小马智行工作,负责优化与部署自动驾驶汽车上的深度学习模型。

Po-Han Huang

Po-Han Huang 是英伟达的深度学习软件工程师。

在过去六年多的时间里,他一直致力于通过 TensorRT 和 CUDA 优化来加速已训练深度神经网络模型的推理。

他拥有伊利诺伊大学厄巴纳-香槟分校的电子与计算机工程硕士学位,专业知识涵盖深度学习加速、计算机视觉和 GPU 架构。

Ben Hamm

Ben Hamm 是英伟达的技术产品经理,专注于 LLM 推理性能与优化。

此前,他曾在亚马逊担任产品经理,负责 Alexa 的唤醒词检测机器学习栈。之后加入 OctoAI 并担任 LLM 托管服务的产品经理。随着公司被收购,他也跟着一起来到了英伟达。

有趣的是,作为一名计算机视觉的爱好者,他甚至还发明了一款 AI 驱动的猫门。

参考资料: